## Features

- Supply Voltage: 8.5V

- RF Frequency Range: 1400 MHz to 1550 MHz

- IF Frequency Range: 150 MHz to 250 MHz

- Enhanced IM3 Rejection

- Overall Gain Control Range: 30 dB Typically

- DSB Noise Figure: 10 dB

- Gain-controlled Amplifier and L-band Mixer

- Power-down Function for the Analog Part

- On-chip Gain-control Circuitry

- On-chip VCO, Typical Frequency 1261.568 MHz

- Internal VCO Can Be Overdriven by an External LO

- On-chip Frequency Synthesizer

- Fixed LO Divider Factor: 2464

- Nine Selectable Reference Divider Factors: 32, 33, 35, 36, 48, 49, 63, 64, 65

- A Reference Oscillator (Can Be Overdriven by an External Reference Signal)

- Tri-state Phase Detector with Programmable Charge Pump

- Programmable Deactivation of Tuning Output

- Lock-status Indication

- Test Interface

## 1. Description

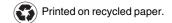

The ATR2730 is a monolithically integrated L-band down-converter circuit fabricated with Atmel's advanced UHF5S technology. This IC covers all functions of an L-band down-converter in a DAB receiver. The device includes a gain-controlled amplifier, a gain-controlled mixer, an output buffer, a gain control block, a power-save function for the analog part, an L-band oscillator, and a complete frequency synthesizer unit. The frequency synthesizer block consists of a reference oscillator/buffer, a reference divider, an RF divider, a tri-state phase detector, a loop filter amplifier, a lock detector, a programmable charge pump, a test interface, and a control interface.

L-band Down-converter for DAB Receivers

# ATR2730

# Preliminary

Rev. 4903A-DAB-03/06

### Figure 1-1. Block Diagram

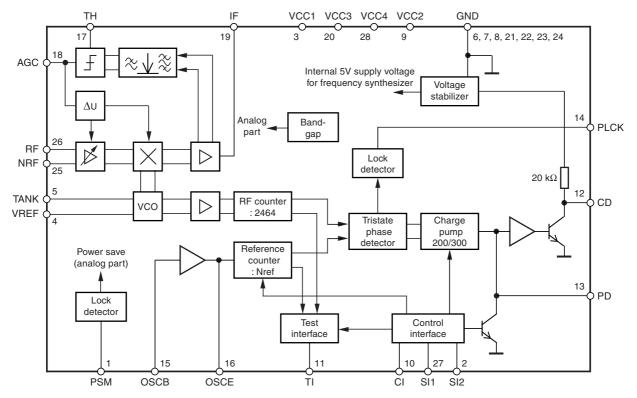

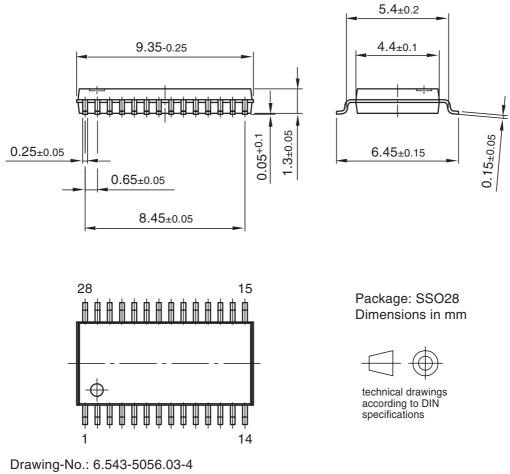

# 2. Pin Configuration

Figure 2-1. Pinning SSO28

| Pin                        | Symbol | Function                                                            |  |  |  |  |

|----------------------------|--------|---------------------------------------------------------------------|--|--|--|--|

| 1                          | PSM    | Power save mode                                                     |  |  |  |  |

| 2                          | SI2    | Control input                                                       |  |  |  |  |

| 3                          | VCC1   | Supply voltage VCO                                                  |  |  |  |  |

| 4                          | VREF   | Reference pin of VCO                                                |  |  |  |  |

| 5                          | TANK   | Tank pin of VCO                                                     |  |  |  |  |

| 6, 7, 8, 21,<br>22, 23, 24 | GND    | Ground                                                              |  |  |  |  |

| 9                          | VCC2   | Supply voltage PLL                                                  |  |  |  |  |

| 10                         | CI     | Control input                                                       |  |  |  |  |

| 11                         | TI     | Test interface                                                      |  |  |  |  |

| 12                         | CD     | Active filter output                                                |  |  |  |  |

| 13                         | PD     | Tri-state charge pump output                                        |  |  |  |  |

| 14                         | PLCK   | Lock-indication output (open collector)                             |  |  |  |  |

| 15                         | OSCB   | Input of internal oscillator/buffer                                 |  |  |  |  |

| 16                         | OSCE   | Output of internal oscillator/buffer                                |  |  |  |  |

| 17                         | TH     | Threshold voltage of comparator                                     |  |  |  |  |

| 18                         | AGC    | Charge-pump output of comparator, AGC input for amplifier and mixer |  |  |  |  |

| 19                         | IF     | Intermediate frequency output                                       |  |  |  |  |

| 20                         | VCC3   | Supply voltage                                                      |  |  |  |  |

| 25                         | NRF    | RF input (inverted)                                                 |  |  |  |  |

| 26                         | RF     | RF input                                                            |  |  |  |  |

| 27                         | SI1    | Control input                                                       |  |  |  |  |

| 28                         | VCC4   | Supply voltage                                                      |  |  |  |  |

**AMEL**<sub>®</sub>

### 3. Functional Description

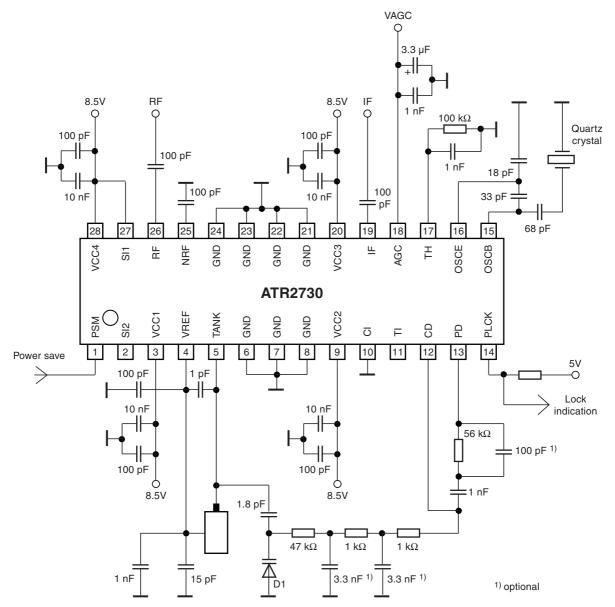

The ATR2730 is an L-band down-converter circuit covering a gain-controlled amplifier, a gain-controlled mixer, an output buffer, a gain control circuitry, an L-band oscillator, and a frequency synthesizer block. Designed for applications in a DAB receiver, the circuit down-converts incoming L-band signals in the frequency range of 1452 MHz to 1492 MHz to an IF frequency in the range of 190 MHz to 230 MHz, which can be handled by a subsequent DAB tuner. A block diagram of this circuit is shown in Figure 1-1 on page 2.

### 3.1 Gain-controlled Amplifier

RF signals applied to the RF input pin are amplified by a gain-controlled amplifier. The complementary pin NRF is not internally blocked; it is recommended to block this pin carefully by an external capacitor. The gain-control voltage is generated by internal gain-control circuitry. The output signal of this amplifier is fed to a gain-controlled mixer.

### 3.2 Gain-controlled Mixer and Output Buffer

The purpose of this mixer is to down-convert the L-band signal in the frequency range of 1452 MHz to 1492 MHz to an IF frequency in the range of about 190 MHz to 230 MHz. Like the amplifier, the gain of the mixer is controlled by the gain-control circuitry. The IF signal is buffered and filtered by a one-pole low-pass filter at a 3 dB frequency of about 500 MHz, and then it is fed to the single-ended output pin IF.

### 3.3 Gain-control Circuitry

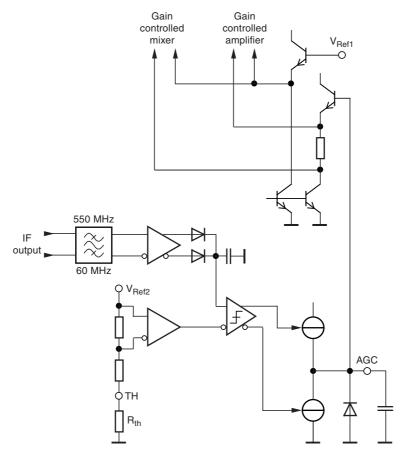

The gain-control circuitry measures the signal power, compares it with a certain power level and generates control voltages for the gain-controlled amplifier and mixer. An equivalent circuit of this functional block is shown in Figure 10-1 on page 14.

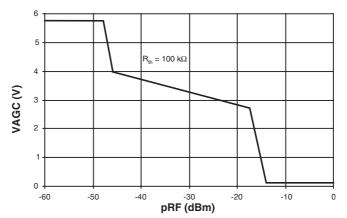

In order to meet this functionality, the output signal of the buffer amplifier is weakly band-pass filtered (transition range of about 60 MHz to 550 MHz), rectified, low-pass filtered, and fed to a comparator whose threshold can be defined by an external resistor, RTH, at pin TH. By varying the value of this resistor, a power threshold of about –33 dBm to –20 dBm can be selected. In order to achieve a good intermodulation ratio, it is recommended to keep the power threshold below –25 dBm. An appropriate application is shown in Figure 8-1 on page 12. Depending on the selection made by the comparator, a charge pump charges or discharges a capacitor which is applied to the AGC pin. By varying this capacitor, different time constants of the AGC loop can be realized. The voltage arising at the AGC pin is used to control the gain setting of the gain-controlled amplifier and mixer. The voltage at pin AGC is in the range of 5.75V for maximum gain and 0.3V for minimum gain. This voltage can be use to control a dual-gate GaAs-FET in front of the ATR2730 to achieve an extended AGC range. By applying an external voltage to the AGC pin, the internal AGC loop can be overdriven.

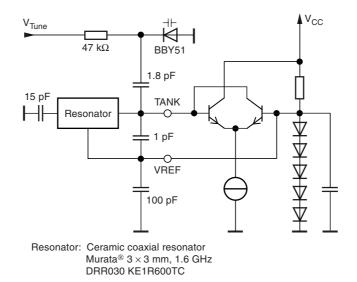

### 3.4 Voltage-controlled Oscillator

A voltage-controlled oscillator supplies an LO signal to the mixer. An equivalent circuit of this oscillator is shown in Figure 10-2 on page 14. In the application circuits (Figure 10-3 on page 15 and Figure 11-1 on page 16), a ceramic coaxial resonator is applied to the oscillator's TANK and VREF pins. It should be noted that  $V_{ref}$  has to be blocked carefully. Figure 11-1 shows a different application where the oscillator is overdriven by an external oscillator. In either case, a DC path at a low impedance must be established between the TANK and VREF pins. The output signal of the oscillator is fed to the LO divider block of the frequency synthesizer unit which locks the VCO's frequency on the frequency of a reference oscillator. Figure 9-1 on page 13 shows the typical phase-noise performance of the oscillator in locked state.

#### 3.5 Overall Properties of the Signal Path

The overall gain of this circuit amounts to 24 dB, the gain-control range is about 30 dB. With a new AGC concept in the amplifier and mixer, the ATR2730 reaches better intermodulation distances (DIM3) at higher IF-output power levels.

#### 3.6 Power Save Mode

For VPSM > 2V (pin 1) the power consumption in the analog part (gain-controlled amplifier and mixer and gain-controlled circuitry) is reduced by 80%. The VCO and the PLL is not influenced by the power-down mode.

#### 3.7 Frequency Synthesizer

The frequency synthesizer block consists of a reference oscillator, a reference divider, an LO divider in order to divide the frequency of the internal oscillator, a tri-state phase detector, a lock detector, a programmable charge pump, a loop filter amplifier, a control interface, and a test interface. The control interface is accessed by three control pins, CI, SI1 and SI2. The test interface provides test signals which represent output signals of the reference and the LO divider.

The purpose of this unit is to lock the frequency  $f_{VCO}$  of the internal VCO on the frequency  $f_{ref}$  of the reference signal applied to the input pin OSCB phase-locked loop according to the following equation:

$f_{VCO} = SF \times f_{ref} / SF_{ref}$

where: SF = 2464,

SF<sub>ref</sub> is the scaling factor of the reference divider according to Table 3-1

| Voltage at Pin SI1 | Voltage at Pin SI2 | SF <sub>ref</sub> | Reference Oscillator<br>Frequency |

|--------------------|--------------------|-------------------|-----------------------------------|

| GND                | OPEN               | 36                | 18.432 MHz                        |

| GND                | VCC                | 33                | -                                 |

| GND                | GND                | 48                | 24.576 MHz                        |

| OPEN               | OPEN               | 65                | -                                 |

| OPEN               | VCC                | 63                | -                                 |

| OPEN               | GND                | 64                | 32.768 MHz                        |

| VCC                | OPEN               | 35                | 17.920 MHZ                        |

| VCC                | VCC                | 32                | 16.384 MHz                        |

| VCC                | GND                | 49                | -                                 |

Table 3-1.

Scaling Factors of the Reference Frequency

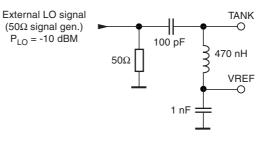

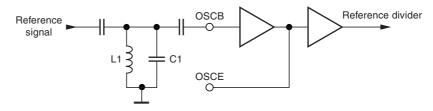

### 3.8 Reference Oscillator

An on-chip crystal oscillator generates the reference signal which is fed to the reference divider. By connecting a quartz crystal to pins OSCE and OSCB according to Figure 11-2 on page 16, this oscillator generates a highly stable reference signal. The ATR2731 (Atmel's one-chip front-end IC) offers the reference signal at pin FREF. This reference signal (LC filtered to suppress harmonics) can be used to overdrive the oscillator. In this application (see Figure 11-3 on page 16) the reference signal has to be applied to the pin OSCB and the pin OSCE must be left open.

### 3.9 Reference Divider

Nine different scaling factors of the reference divider can be selected by different voltage settings at the input pins SI1 and SI2: 32,  $33^{(1)}$ , 35, 36, 48,  $49^{(1)}$ ,  $63^{(1)}$ , 64,  $65^{(1)}$ . The reference divider factors result in reference oscillator frequencies shown in Table 3-1.

Note: 1. These scaling factors result in an output frequency of the reference divider of 512 kHz. If harmonics of the Bd. 3 VCO fall in the L-band reception band, these spurious signals can influence the AGC of ATR2730, which could be a problem for small incoming signals. In this case it is possible to switch the reference divider from  $n_{ref}$  to  $n_{ref} + 1$ .

### 3.10 LO Divider

The LO divider is operated at the fixed division ratio 2464. Assuming the settings described in the section "Reference Divider", the oscillator's frequency is controlled to be 1261.568 MHz in the locked state, and the output frequency of the RF divider is 512 kHz.

### 3.11 Phase Comparator, Charge Pump and Loop Filter

The tri-state phase detector causes the charge pump to source or sink current at the output pin PD depending on the phase relation of its input signals, which are provided by the reference and the RF divider respectively. Using the control pin CI, two different values of this current can be selected, and the charge-pump current can be switched off.

The input of the high-gain amplifier (output pin CD), which is implemented in order to construct a loop filter as shown in the application circuit, can be switched to GND by means of the control pin CI (see Table 3-2 on page 8). In the application circuit, the loop filter is completed by connecting the pins PD and CD by an appropriate RC network.

### 3.12 Lock Detector

An internal lock detector checks if the phase difference of the input signals of the phase detector is smaller than approximately 250 ns in seven subsequent comparisons. If a phase lock is detected, the open collector output pin PLCK is set to HIGH. It should be noted that the output current of this pin must be limited by external circuitry as it is not limited internally. If the voltage at the control pin CI is chosen to be half the supply voltage, or if this control pin is left open, the lock-detector function is deactivated and the logical value of the PLCK output is undefined.

### 3.13 Test Interface

If the input control pin CI is left open (high impedance state), a test signal, which monitors the output frequency of the reference divider, appears at the output pin TI.

Analogous to the reference divider, a test signal monitoring the output frequency of the RF divider appears at the test interface output pin TI, if the input control pin CI is connected to  $V_{CC}/2$ .

| CI                 | PD               | PLCK      | TI                |

|--------------------|------------------|-----------|-------------------|

| GND                | 200 µA           | Ok        | -                 |

| V <sub>s</sub>     | 300 µA           | Ok        | -                 |

| V <sub>CC</sub> /2 | 0 µA             | Undefined | RF divider        |

| Open               | Connected to GND | Undefined | Reference divider |

Table 3-2.

Control Interface (CI) Settings

# 4. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                                    | Pins                                  | Symbol            | Value        | Unit             |

|---------------------------------------------------------------|---------------------------------------|-------------------|--------------|------------------|

| Supply voltage                                                | Itage 3, 9, 20 and 28 V <sub>CC</sub> |                   | -0.3 to +9.5 | V                |

| RF input voltage                                              | 25 and 26                             | V <sub>RF</sub>   | 750          | mV <sub>pp</sub> |

| Voltage at pin AGC                                            | 18                                    | V <sub>AGC</sub>  | 0.5 to 6     | V                |

| Voltage at pin TH                                             | 17                                    | V <sub>TH</sub>   | -0.3 to +4.0 | V                |

| Input voltage at pin TANK<br>(internal oscillator overdriven) |                                       |                   | 1            | V <sub>pp</sub>  |

| Current at IF output                                          | 19                                    | I <sub>IF</sub>   | 4.0          | mA               |

| Reference input voltage (diff.)                               | 15                                    | OSCB              | 1            | V <sub>pp</sub>  |

| Control input voltage                                         | 1, 2, 10 and 27                       | CI, SI1, SI2, PD  | -0.3 to +9.5 | V                |

| PLCK output current                                           | 14                                    | I <sub>PLCK</sub> | 0.5          | mA               |

| PLCK output voltage                                           | 14                                    | V <sub>PLCK</sub> | -0.3 to +5.5 | V                |

| Junction temperature                                          |                                       | Τ <sub>j</sub>    | 125          | °C               |

| Storage temperature                                           |                                       | T <sub>stg</sub>  | -40 to +125  | °C               |

### 5. Operating Range

| Parameters          | Pins            | Symbol           | Value      | Unit |

|---------------------|-----------------|------------------|------------|------|

| Supply voltage      | 3, 9, 20 and 28 | V <sub>CC</sub>  | 8 to 9.35  | V    |

| Ambient Temperature |                 | T <sub>amb</sub> | -40 to +85 | °C   |

## 6. Thermal Resistance

| Parameters                    | Symbol            | Value | Unit |

|-------------------------------|-------------------|-------|------|

| Junction ambient SSO28 (mod.) | R <sub>thJA</sub> | 50    | K/W  |

| <u> </u> |   |

|----------|---|

|          | R |

# 7. Electrical Characteristics

Operating conditions:  $V_{CC} = 8.5V$ ,  $T_{amb} = 25^{\circ}C$  unless otherwise specified. (See application circuit Figure 10-3 on page 15.)

| No. | Parameters                               | Test Conditions                                                                | Pin           | Symbol                 | Min.     | Тур.     | Max. | Unit     | Type*  |

|-----|------------------------------------------|--------------------------------------------------------------------------------|---------------|------------------------|----------|----------|------|----------|--------|

| 1.1 | Supply current (max. gain)               | p <sub>RF</sub> =60 dBm<br>V <sub>PSM</sub> < 0.5V                             |               | I <sub>S,MAX</sub>     |          | 40       | 48   | mA       | А      |

| 1.2 | Supply current (min. gain)               | p <sub>RF</sub> = -10 dBm<br>V <sub>PSM</sub> < 0.5V                           |               | I <sub>S,MIN</sub>     |          | 41       | 50   | mA       | В      |

| 1.3 | Supply current<br>(power-save mode)      | $p_{RF} = -10 \text{ dBm}$<br>$V_{PSM} > 2V$                                   |               | I <sub>S,PD</sub>      |          | 20       | 24   | mA       | А      |

| 2   | Amplifier Mixer Pin 26                   |                                                                                | <b>26 →19</b> |                        |          |          |      |          |        |

| 2.1 | Maximum conversion gain                  | p <sub>RF</sub> =60 dBm                                                        |               | g <sub>c,max</sub>     | 20       | 24       |      | dB       | Α      |

| 2.2 | Minimum conversion gain                  | p <sub>RF</sub> =15 dBm                                                        |               | g <sub>c,min</sub>     |          | -8       |      | dB       | В      |

| 2.3 | AGC range                                |                                                                                |               | $\Delta g_{c}$         | 28       | 32       |      | dB       | Α      |

| 2.4 | Third-order 2-tone intermodulation ratio | $p_{RF1} + p_{RF2} = -10 \text{ dBm}$<br>$p_{RF1} + p_{RF2} = -15 \text{ dBm}$ |               | dim3                   | 30<br>35 | 35<br>40 |      | dB<br>dB | B<br>A |

| 2.5 | DSB noise figure<br>(50Ω system)         | Maximum gain<br>Minimum gain                                                   |               | NF                     |          | 10<br>30 |      | dB<br>dB | D      |

| 3   | RF Input                                 |                                                                                | 26            |                        |          |          |      |          |        |

| 3.1 | Frequency range                          |                                                                                |               | f <sub>in,RF</sub>     | 1400     |          | 1550 | MHz      | С      |

| 3.2 | Maximum input power                      | dim3 ≥20 dB                                                                    |               | p <sub>in,max,RF</sub> |          | -6       |      | dBm      | С      |

| 3.3 | Input impedance                          |                                                                                |               | Z <sub>in,RF</sub>     |          | 200    1 |      | Ωll pF   | D      |

| 4   | IF Output                                |                                                                                | 19            | _Li                    |          |          |      |          |        |

| 4.1 | Frequency range                          |                                                                                |               | f <sub>out,IF</sub>    | 150      |          | 250  | MHz      | С      |

| 4.2 | Output impedance                         |                                                                                |               | Z <sub>out,IF</sub>    |          | 50       |      | Ω        | D      |

| 4.3 | Voltage standing wave ratio              |                                                                                |               | VSWR <sub>IF</sub>     |          | 2.0      |      |          | D      |

| 5   | Gain Control                             |                                                                                | 1             | 1                      |          | I        |      |          |        |

| 5.1 | Threshold adjustment                     | External resistor                                                              | 17            | R <sub>TH</sub>        |          | 100      |      | kΩ       | D      |

| - 0 |                                          | $p_{RF} = -10 \text{ dBm}$<br>$V_{AGC} = 3.5 \text{V}$                         | 18            | I <sub>CP,P</sub>      | 75       | 100      | 125  | μA       | А      |

| 5.2 | Charge pump current                      | $p_{RF} = -60 \text{ dBm}$<br>$V_{AGC} = 3.5 \text{V}$                         |               | I <sub>CP,N</sub>      | -125     | -100     | -75  | μΑ       | А      |

| 5.3 | Minimum gain control voltage             | p <sub>RF</sub> =10 dBm                                                        | 18            | V <sub>AGCmin</sub>    |          | 0.1      | 0.6  | v        | А      |

| 5.4 | Maximum gain control voltage             | p <sub>RF</sub> =60 dBm                                                        | 18            | V <sub>AGC</sub> max   | 5.5      | 5.75     |      | v        | А      |

| 6   | VCO                                      |                                                                                | 5             |                        |          |          |      |          |        |

| 6.1 | Frequency                                |                                                                                |               | f <sub>LO</sub>        | 1000     | 1261.568 | 1500 | MHz      |        |

| 6.2 | Phase noise                              | 1 kHz distance                                                                 |               | L <sub>1kHz</sub>      |          | -75      |      | dBc/Hz   | С      |

| 6.3 | Minimum input power                      | VCO overdriven, see                                                            |               | p <sub>LO,MIN</sub>    |          | -11      |      | dBm      | С      |

| 6.4 | Maximum input power                      | "Application Circuit" (Figure<br>10-3 on page 15)                              |               | p <sub>LO,MAX</sub>    |          | -5       |      | dBm      | С      |

| 7   | Frequency Synthesizer                    |                                                                                |               |                        |          |          |      |          |        |

| 7.1 | RF divide factor                         |                                                                                |               | SF                     |          | 2464     |      |          | Α      |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

# 7. Electrical Characteristics (Continued)

Operating conditions:  $V_{CC} = 8.5V$ ,  $T_{amb} = 25^{\circ}C$  unless otherwise specified. (See application circuit Figure 10-3 on page 15.)

| No.  | Parameters                   | Test Conditions                                                                                                                                                                                                                                                                                                                | Pin      | Symbol                               | Min.       | Тур.                                               | Max.       | Unit              | Type*  |

|------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------|------------|----------------------------------------------------|------------|-------------------|--------|

| 7.2  | Reference divide factor      | $\begin{array}{l} SI1 = GND, SI2 = GND\\ SI1 = GND, SI2 = VCC\\ SI1 = GND, SI2 = open\\ SI1 = VCC, SI2 = GND\\ SI1 = VCC, SI2 = VCC\\ SI1 = VCC, SI2 = open\\ SI1 = open, SI2 = GND\\ SI1 = open, SI2 = VCC\\ SI1 = open, SI2 = open\\ \end{array}$ |          | SF <sub>ref</sub>                    |            | 48<br>33<br>36<br>49<br>32<br>35<br>64<br>63<br>65 |            |                   | A      |

| 7.3  | Input frequency range        |                                                                                                                                                                                                                                                                                                                                |          | f <sub>ref</sub>                     | 5          |                                                    | 50         | MHz               | С      |

| 7.4  | Input sensitivity            |                                                                                                                                                                                                                                                                                                                                | 15       | V <sub>refs</sub>                    |            |                                                    | 30         | mV <sub>rms</sub> | С      |

| 7.5  | Maximum input signal         | ·                                                                                                                                                                                                                                                                                                                              |          | V <sub>refmax</sub>                  |            | 300                                                |            | mV <sub>rms</sub> | С      |

| 7.6  | Input impedance              | Single-ended                                                                                                                                                                                                                                                                                                                   |          | Z <sub>ref</sub>                     |            | 2.7k    2.5                                        |            | kΩ    pF          | D      |

| 8    | Phase Detector               | -                                                                                                                                                                                                                                                                                                                              |          |                                      |            |                                                    |            |                   |        |

| 8.1  | Charge-pump current          | Pin CI connected to GND Pin CI connected to $V_{CC}$                                                                                                                                                                                                                                                                           | 13       | I <sub>PD2</sub><br>I <sub>PD1</sub> | 160<br>240 | 200<br>300                                         | 240<br>360 | μΑ<br>μΑ          | A<br>A |

|      |                              | Pin CI connected to $V_{CC}/2$                                                                                                                                                                                                                                                                                                 |          | I <sub>PD1,tri</sub>                 |            |                                                    | 100        | nA                | A      |

| 8.2  | Output voltage PD            | Pin CI open                                                                                                                                                                                                                                                                                                                    | 13       | V <sub>PD</sub>                      |            |                                                    | 0.3        | V                 | A      |

| 8.3  | Internal reference frequency |                                                                                                                                                                                                                                                                                                                                |          | f <sub>PD</sub>                      |            | 512                                                |            | kHz               | В      |

| 8.4  | Typical tuning voltage range |                                                                                                                                                                                                                                                                                                                                | 12       | V <sub>tune</sub>                    | 0.3        |                                                    | 5          | V                 | С      |

| 9    | Lock Indication PLCK         | Γ                                                                                                                                                                                                                                                                                                                              | 14       |                                      |            | 1                                                  |            | 1                 |        |

| 9.1  | Leakage current              | $V_{PLCK} = 5.5V$                                                                                                                                                                                                                                                                                                              |          | I <sub>PLCK</sub>                    |            |                                                    | 10         | μΑ                | A      |

| 9.2  | Saturation voltage           | I <sub>PLCK</sub> = 0.25 mA                                                                                                                                                                                                                                                                                                    |          | V <sub>PLCK,sat</sub>                |            |                                                    | 0.5        | V                 | Α      |

| 10   | Control Inputs SI            | 1                                                                                                                                                                                                                                                                                                                              | 2 and 27 |                                      | n          |                                                    |            |                   | 1      |

| 10.1 |                              | Pin connected to GND                                                                                                                                                                                                                                                                                                           |          | VL                                   | 0          |                                                    | 0.1        | V <sub>CC</sub>   | Α      |

| 10.2 | Input voltage                | Pin open                                                                                                                                                                                                                                                                                                                       |          | V <sub>M</sub>                       |            | Open                                               |            |                   | Α      |

| 10.3 |                              | Pin connected to $V_{\text{CC}}$                                                                                                                                                                                                                                                                                               |          | V <sub>H</sub>                       | 0.9        |                                                    | 1          | V <sub>CC</sub>   | Α      |

| 11   | Control Input CI             |                                                                                                                                                                                                                                                                                                                                | 10       |                                      |            |                                                    |            |                   |        |

| 11.1 |                              | Pin connected to GND                                                                                                                                                                                                                                                                                                           |          | $V_L$                                | 0          |                                                    | 0.1        | V <sub>CC</sub>   | Α      |

| 11.2 | Input voltage                | Pin connected to $V_{CC}/2$                                                                                                                                                                                                                                                                                                    |          | V <sub>M</sub>                       |            | 0.5                                                |            | V <sub>CC</sub>   | Α      |

| 11.3 | input voltago                | Pin open                                                                                                                                                                                                                                                                                                                       |          | V <sub>open</sub>                    |            | Open                                               |            |                   | Α      |

| 11.4 |                              | Pin connected to $V_{CC}$                                                                                                                                                                                                                                                                                                      |          | V <sub>H</sub>                       | 0.9        |                                                    | 1          | V <sub>CC</sub>   | Α      |

| 12   | Test Interface TI            |                                                                                                                                                                                                                                                                                                                                | 11       |                                      |            |                                                    |            |                   |        |

| 12.1 | Reference test frequency     | Pin CI open                                                                                                                                                                                                                                                                                                                    |          | f <sub>test,ref</sub>                |            | 512                                                |            | kHz               | В      |

| 12.2 | LO test frequency            | $Pin CI = V_{CC}/2$                                                                                                                                                                                                                                                                                                            |          | f <sub>test,LO</sub>                 |            | 512                                                |            | kHz               | В      |

| 12.3 | Voltage swing                | $\begin{array}{l} R_{load} \ \geq 1 \ M\Omega, \ C_{load} \leq 15 \ p\text{F}, \\ Pin \ Cl \ open \ or \ V_{CC}/2 \end{array}$                                                                                                                                                                                                 |          | V <sub>sw</sub>                      |            | 400                                                |            | mV <sub>pp</sub>  | С      |

| 13   | Power-save Mode PSM          |                                                                                                                                                                                                                                                                                                                                | 1        |                                      |            |                                                    |            |                   | -      |

| 13.1 |                              | PSM not active                                                                                                                                                                                                                                                                                                                 |          | V <sub>PSM</sub>                     |            |                                                    | 0.6        | V                 | Α      |

| 13.2 |                              | PSM active                                                                                                                                                                                                                                                                                                                     |          | V <sub>PSM</sub>                     | 2.0        |                                                    |            | V                 | Α      |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

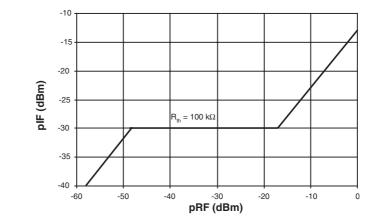

### 8. Gain Control Characteristics

Operating conditions: V\_{CC} = 8.5V, T\_{amb} = 27° C, f\_{RF} = 1490 MHz, F\_{LO} = 1261.568 MHz

Figure 8-2. Gain Control Voltage (Pin 11)

## 9. Phase-noise Performance

Measurement conditions:

Values acquired at pin 19 with HP 70000 spectrum analyzer. RF input (pin 26) is blocked with 100 pF to GND.

A low phase-noise signal generator (Marconi<sup>®</sup> 2042) was taken as PLL reference.

**Figure 9-1.** Phase-noise Performance Operating Conditions:  $f_{REF} = 17.92 \text{ MHz}, -10 \text{ dB},$  $I_{PD} = 200 \ \mu\text{A}$

|               | 29 dBm<br>I 10 dB<br>IB/DIV |        |         |        |     |          |          |         |    |                                                |           |

|---------------|-----------------------------|--------|---------|--------|-----|----------|----------|---------|----|------------------------------------------------|-----------|

|               |                             |        |         |        |     |          |          |         | -  |                                                |           |

|               |                             |        |         |        |     |          |          |         |    |                                                |           |

|               |                             |        |         |        |     |          |          |         | <  | < -75 dBc/ŀ                                    | łz        |

|               |                             |        |         |        |     |          |          |         |    |                                                |           |

|               |                             |        | whenter | hutter | MAN | (ulmater | WWWWWWWW |         | L  |                                                |           |

| n i uinda     | When all the state          | WWWWWW | W. W.   |        |     |          |          | MAN MAN | ## | WANT ALANA AND AND AND AND AND AND AND AND AND |           |

| H-A-MALANAR A |                             |        |         |        |     |          |          |         |    |                                                | Mr HMA/44 |

|               |                             |        |         |        |     |          |          |         |    |                                                |           |

|               |                             |        |         |        |     |          |          |         |    |                                                |           |

|               |                             |        |         |        |     |          |          |         |    |                                                |           |

Center 1.261 568 GHz RB 100 Hz VB 100 Hz Span 50.00 kHz

ST 15.00 sec

## **10. Equivalent Circuits**

Figure 10-1. AGC Control Circuit

Figure 10-2. VCO Circuit

Figure 10-3. Application Circuit

Example: reference divider factor = 35,  $f_{\text{REF}}$  = 17.92 MHz, charge-pump current = 200  $\mu\text{A}$

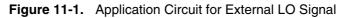

# **11. Application Circuit for External LO Signal**

With an external LO signal it is possible to overdrive the VCO. In this case, the internal VCO acts as an LO buffer.

#### Figure 11-3. Reference Oscillator Overdriven

# **12. Ordering Information**

| Extended Type Number | Package | Remarks                                          |

|----------------------|---------|--------------------------------------------------|

| ATR2730-TCSY         | SSO28   | Tube, Pb-free                                    |

| ATR2730-TCQY         | SSO28   | Taped and reeled according to IEC 286-3, Pb-free |

## 13. Package Information

Issue: 1; 10.03.04

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

Memory 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2006. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.